### **Deep Cryogenic Temperature CMOS Circuit and System Design for Quantum Computing Applications**

Jency Rubia J<sup>1,\*</sup>, Sherin Shibi C<sup>2</sup>, Rosi A<sup>1</sup>, Babitha Lincy R<sup>3</sup> and Ezhil E Nithila<sup>1</sup>

<sup>1</sup>Vel Tech Rangarajan Dr.Sagunthala R&D Institute of Science and Technology, Avadi, India

<sup>2</sup>SRM Institute of Science and Technology, Kattankulathur, Tamil Nadu, India

<sup>3</sup>Sri Eshwar College of Engineering, Coimbatore, India

### Abstract

Quantum computing is a fascinating and rapidly evolving field of technology that promises to revolutionize many areas of science, engineering, and society. The fundamental unit of quantum computing is the quantum bit that can exist in two or more states concurrently, as opposed to a classical bit that can only be either 0 or 1. Any subatomic element, including atoms, electrons, and photons, can be used to implement qubits. The chosen sub-atomic elements should have quantum mechanical properties. Most commonly, photons have been used to implement qubits. Qubits can be manipulated and read by applying external fields or pulses, such as lasers, magnets, or microwaves. Quantum computers are currently suffering from various complications such as size, operating temperature, coherence problems, entanglement, etc. The realization of quantum computing, a novel paradigm that uses quantum mechanical phenomena to do computations that are not possible with classical computers, is made possible, most crucially, by the need for a quantum processor and a quantum SOC. As a result, Cryo-CMOS technology can make it possible to integrate a Quantum system on a chip. Cryo-CMOS devices are electronic circuits that operate at cryogenic temperatures, usually below 77 K (-196 °C).

Keywords: cryo-CMOS, quantum SOC, quantum processor, scalability, IC design, performance analysis

Received on 09 January 2023, accepted on 22 January 2024, published on 01 February 2024

Copyright © 2024 Jency Rubia J *et al.*, licensed to EAI. This is an open access article distributed under the terms of the <u>CC BY-NC-SA 4.0</u>, which permits copying, redistributing, remixing, transformation, and building upon the material in any medium so long as the original work is properly cited.

doi: 10.4108/ew.4997

#### 1. Introduction

In order to solve several computing issues related to medication discovery, cybersecurity, climate predicting, etc., quantum computers can offer exponential speedup. At present, quantum computers run with just 50 qubits. In this range itself, quantum computer surpasses supercomputers in specific applications. However, functional, practical applications would require millions of qubits. The connection concerns solid-state qubits operating at 20 milli Kelvin within dilution refrigerators and control electronics. The control electronics modules are located outside the dilution refrigerator. The controller's location outside is one of the main challenges to scaling from 50 qubits to millions of qubits. Long coaxial cables connect these electronics. A 50qubit processor requires hundreds of connections, digital to analogue converters, mixers, and amplifiers. The system's scalability issue became more acute in this situation. Most of the IC manufacturing industries and companies give their attention towards realizing quantum computing using CMOS technology. Since our world relies on classical computing, quantum computing is based on quantum mechanics. Thus, various quantum researchers try to control quantum bits utilizing CMOS technology. If that is possible, the size and operating temperature of the quantum computer can be scale down for practical applications. The solution to the problem as mentioned above is using cryogenic integrated circuit design across devices, circuits and systems.

<sup>\*</sup>Corresponding author. Email: jencyrubia@gmail.com

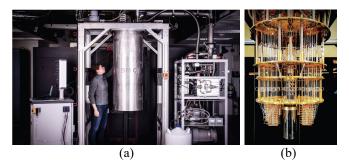

Integrating millions of millions MOS transistors in a single chip is called VLSI technology. When deep submicron CMOS circuits have been designed, the effect of quantum tunnelling will happen. A subatomic particle can sometimes pass through a potential barrier that is typically impossible due to quantum tunnelling. In very-large-scale integration (VLSI) electronics, quantum tunnelling is a cause of current leakage, resulting in significant power drain and thermal effects that afflict such devices. It is regarded as the bare minimum for producing microelectronic device components. Cryo-CMOS is a CMOS technology that operates at deepcryogenic temperatures (below 77 K) for quantum computing applications. Cryo-CMOS circuits can achieve sub thermionic subthreshold swing (SS), which allows supply voltage scaling while maintaining a high ON-OFF current ratio. Cryo-CMOS can also exploit enhanced carrier mobility and reduced parasitic capacitance at low temperatures to improve the device's performance. Therefore, cryo-CMOS can overcome the quantum tunnelling effect in VLSI by lowering the current leakage and power consumption and increasing the device speed and scalability. However, there are still many challenges and limitations in designing and operating cryo-CMOS for quantum computing applications, such as device modelling, noise cancellation, system integration, and reliability. Figure 1 shown real-time quantum computer and the dilution refrigerator.

**Figure 1.** A typical superconducting quantum computer (a) Dilution Refrigerator (cooling center) (b) The interior of a refrigerator for multistage dilution

There are no clear signal standards because dilution refrigerators only permit a certain amount of power dissipation. Hence designing cryogenic qubit controllers is difficult. Building circuits for high-fidelity control requires accurate modelling of qubit controllers and qubit gate operations. Creating application-specific integrated circuits that dissipate less power would make it possible. To determine the accuracy and allowable noise of the signals for high-fidelity qubit control, the work can use a co-simulated behavioural microwave signal generator and a Hamiltonianbased model of the quantum processor.

This study gives a general introduction of the concept of quantum computing, as well as the opportunities and problems that cryo-CMOS technology faces in enabling scalable quantum computers. Additionally, examples of cryoCMOS circuits and systems, including low-noise amplifiers, oscillators, voltage references, and data converters, are shown. This article also discusses the obstacles and future directions for cryo-CMOS technology research, including power dissipation, variability, mismatch, noise, and device modeling. The following is how the work is structured. The fundamentals of quantum computing and the reasons for this research are covered in Section II. The theoretical underpinnings of cryo-CMOS and the implementation of quantum processors are revealed in Section III. Section IV presents a comprehensive summary of the current quantum computers as well as the research gaps. Future research directions are provided in Section V, which wraps up the essay.

### 2. Basics of Quantum Computing

The classical computer operates based on bits, originates from binary digit. The binary digit can store 0 or 1. But, in a quantum computer, the basic information is quantum bit (qubit). The qubit can attain 0 and 1 state at the same time. The property of existing a qubit in both states (0 and 1) is known as superposition. The superposition state of the qubit supports parallel computation in quantum computing. The feature of parallelism allows an N-qubit computer to encode 2N bits of information simultaneously [1]. But, in classical computer, N-bits information can be encoded N-bits only. Entanglement, or the inseparability of the state of two or more qubits, is another characteristic of qubits that sets them apart from classical bits [2]. Since coupling could negatively impact the state of one bit due to undesired noise from the other bits, the classical bits are often uncoupled and isolated from one another. However, when two qubits are coupled or entangled, their behaviours are correlated, meaning that any change in one qubit's state will predictably alter the other qubit's state. A quantum algorithm uses the unique superposition and entanglement capabilities of qubits to produce exponential speedups over classical computers in some calculations.

Another important application of quantum computing is an act in quantum chemistry. Because the quantum processor's mapping of molecular structures allowed for the simulation of molecular interaction [3]. As a result, it is possible to create new chemicals and chemical processes while improving existing ones. The calibre and number of qubits directly impact a quantum processor's power. Even the most powerful supercomputers have been outperformed by a quantum computer with only 53 qubits. However, for such practical applications, large-scale quantum computers with hundreds or even millions of qubits would be required [4]. This necessitates the development of a scalable architecture for deploying control electronics and qubits, the two fundamental components of a quantum computer.

### 2.1. Towards Scalability

Currently, qubits can be implemented with trapped ions [5] and bulk nuclear magnetic resonance [6]. As time passed, realized that a scalable qubit architecture is required to have a quantum computer with hundreds of qubits. The characteristics of implanting quantum effects in solid-state qubit technologies are known as superconducting qubits [7]. The development of superconducting qubits paved the way towards a scalable architecture because of their feasibility in semiconductor fabrication. Thus, it supports scalability. By using a microwave pulse, the superconducting qubit states may be read out. These qubits must operate at a cryogenic temperature of around 10 m K, which can be maintained inside a dilution refrigerator.

In order to maintain the qubit's quantum characteristics, the Josephson junction must function at this temperature [8]. Two superconductors separated by a small insulating layer make up a Josephson junction. Tunnelling, a quantum mechanical phenomenon, enables a supercurrent to flow across the junction without any applied voltage. Josephson junctions are helpful for quantum computing because they can function as qubits, the fundamental building blocks of quantum information. Qubits can be created and modified by adjusting the phase and charge of the Josephson junction [9]. Josephson junctions are generally desirable candidates for quantum computing due to their low dissipation, high nonlinearity, and compatibility with methods of fabricating integrated circuits.

Unlike superconducting qubits, which require the creation of an artificial atom, spin qubits store information in the spin of a single electron. By sending a microwave pulse with a frequency equal to the Zeeman energy, the qubit states are altered. Because it impacts the Zeeman effect, which splits an atom's spectral lines in the presence of an external magnetic field, Zeeman energy is crucial for quantum computing. To regulate the magnetic field between qubits, the Zeeman effect can be used. This influences the qubit states. Through spinto-charge conversion, spin-selective tunnelling between a dot and the reservoir, or Pauli spin blocking, the states can be read out. These qubits must also operate at cryogenic temperatures, although they have a wider operational temperature range, going up to 5 K [10-11].

### 2.2. Motivation of Scalability

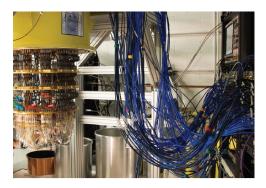

The scalability of qubits is not only used for system compactness but also for control electronics. In a dilution refrigerator, where qubits commonly operate, the control electronics are typically built with hardware. The equipment is kept at ambient temperature and is situated outside of the surroundings. Each qubit has at least one RF link to the controller hardware. Due to the excessive complexity of an equipment-based control, such control topologies restrict scalability. Additionally, a lot of wires and cables must be constructed. Consequently, it would be impossible to fit hundreds of cables inside a tiny refrigerator while also lowering the freezer's heat load and preserving the integrity of the interconnects. Figure 2 shows that the longest state-ofthe-art quantum computer (with 72 qubits) needs 168 long and lossy coaxial cables to connect cryogenic qubits to various big, cumbersome, specially made electrical modules that are running at RT (DAC, LNA, ADC, etc.).

### Figure 2. superconducting qubits in a cutting-edge quantum computer [12]

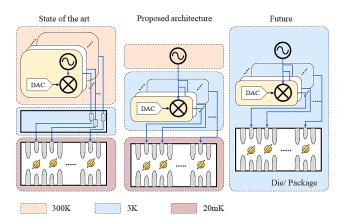

For large-scale quantum computers, operating qubits and control circuits at the same cryogenic temperature would be ideal [13]. Complex circuits can be created using CMOS as transition from the vacuum tube era to the IC era, taking advantage of 60 years of advancement in IC design technology. These ICs must function at deep cryogenic temperatures and use power within the limitations of the refrigerator in order to be integrated with the qubit chip, as shown in Figure 3. Custom PCBs have been built to link many control and read-out channels while minimizing cabling, using commercially available components that operate at cryogenic temperatures [14–15].

Figure 3. General concept of the present research direction

### 3. Overview of Cryo-CMOS Qubit

A quantum computer consists of a regular electronic controller with a cryogenic quantum processor. Any useful quantum algorithm requires cryogenic quantum processors to be scaled down to a minimum of a few thousand and most likely millions of qubits. the requirement of cryo-CMOS circuits, which give the controller and the quantum processor useful and compact linkages. Cryo-CMOS is a method that enables the development of semiconductor intellectual property (IP) that can operate at or below zero Kelvin (-273.15 °C) or at cryogenic temperatures. The fundamental components of quantum computers are quantum bits, or qubits. They enable the execution of multiple complicated problems concurrently while storing and processing data in a superposition state. Qubits are extremely sensitive to noise and interference and must function at very low temperatures. Current quantum computer designs separate the control circuitry from the qubits and connect them using thick, cabling. Quantum computing systems' expensive performance and scalability are constrained as the number of qubits increases. This problem is addressed by cryo-CMOS technology, which enables the creation of unique chips that can communicate with qubits at cryogenic temperatures, hence requiring less cabling and increasing the effectiveness and dependability of quantum computing systems.

A promising technique called cryo-CMOS has the potential to hasten the creation and application of quantum computers in various fields, including research, medicine, logistics, finance, and artificial intelligence. However, there are still some difficulties and chances for more study and invention in this area, like improving the design procedures, equipment, and guidelines for cryo-CMOS IP development.

## 3.1. Cryo-CMOS Control: A Key Technology for Quantum Computing

On qubits, numerous physical implementations have been made. However, solid-state implementation is thought to be one of the most viable options for scaling down a significant number of qubits [16]. Additionally, several types of solidstate qubits exist, including nitrogen vacancies in diamond lattices, electron spins in quantum dot applications and superconducting circuits. The operating temperature is a characteristic shared by all qubit variant kinds. Only temperatures below 100 m K for deep cryogenic operation suit these variations. The cryogenic temperature allows them to exchange their quantum behaviours with each other and maintain their quantum state's coherence time [17]. In general, the coherence times withstand only below a second, which is much less for processing practical quantum algorithms. Modern quantum processors use a small number of qubits, whereas most circuits use classical controllers that function at average temperatures. Wires from the conventional controller connect the qubits in the cryogenic container. Some functionality has so far been started that operates at cryogenic temperatures, such as low noise amplifiers (LNAs) for reading out signals and signal

attenuation [18]. Closer proximity operating of cryogenic temperature was the only thing that was accomplished. There might be a need for many cables if the number of qubits were to expand. The error-correction loop's thermal load and delay are thus increased [19]. To connect a room-temperature quantum processor to a cryogenic quantum processor in a quantum computer, thousands of low- and high-frequency wires are now necessary. This would lead to an expensive procedure that could have been more practical and dependable.

Alternative cryogenic controllers were required to overcome the abovementioned problems and decrease the requirements, system size, and dependability. Cryogenic testing has been performed on a wide range of technologies, including compound semiconductors (GaAs), JFET (junction field effect transistors), HEMT (high electron mobility transistors), superconducting devices based on Josephson junctions, and CMOS transistors [20]. Based on developments in the semiconductor industry, research suggests that CMOS technology may guarantee low power consumption and functioning down to 30 mK [21]. Future quantum processor complexity may be regulated due to the practicality of packing billions of transistors into a single chip. Another argument favouring its use is that the design automation framework for CMOS is well adapted to the typical manufacturing and armed temperature values, i.e., down to -55 °C.

### 3.2. Architecture of Cryo-CMOS Processor & Controller

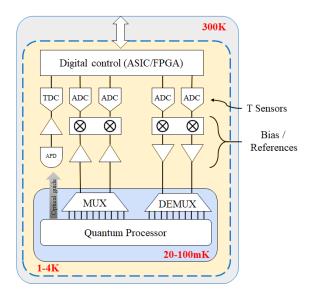

The general layout of a quantum processor's control and readout is shown in Figure 4. The architecture includes frontend and back-end modules. The front-end module is responsible for multiplexing, demultiplexing, and analog to digital and digital to analog conversion. The ADC/DAC is essential for the analogue signal that is delivered to and received from all qubits. In a perfect world, electronics and quantum processors would both function at the same temperature. To avoid the necessity for off-board communication, both should if not be on the same chip. It is already possible to decrease temperatures below 100 mK with less than 1 mW of power [22], but it is as of yet uncertain if a full electronic controller can quickly function with such a power budget.

Figure 4. Quantum processor control and readout

The system would run in the 4 K stage if the cooling power was greater than 1 W. Some low-power components may lower the number of connections to the 4-K stages. As seen in Figure 4, such features are anticipated to operate at a temperature comparable to that of the quantum processor. The cryo-CMOS electronics controller's specifications are very enticing. The current generation of quantum processors uses electric pulses to determine the state of the qubits. The amplitude, timing, frequency, and phase of the electronic signals that measure the states must be highly exact. Additionally, the noise generated by the signal should be minimal. However, Modern quantum processors are controlled by the most precise bench-top electrical instrumentation on the market [17-18]. The controller's readout must be extremely sensitive to pick up faint signals from the quantum processor [23]. Moreover, it should attain low kickback to avoid modification in qubit states. The phenomenon known as kickback in quantum mechanics occurs when one qubit or register's phase is transferred to another without changing the first qubit or register. The quantum processor and controller specification meet the criteria if the error-correction loop's latency is less than the qubit coherence time. The controller must retain the abovementioned functionality and standards while dissipating minimal power. The power budget for a processing unit with only 1000 qubits would be limited to 1 mW/qubit. That operation is so complex, as shown in [23. Even when more than 1-W of cooling power is provided at 4 Κ.

Therefore, even if a 1 mW/qubit power budget is ambitious, it is unquestionably feasible in the near and medium term. The advancement of improved cryo-CMOS systems must coexist with the development of more advanced and potent cooling technologies. In addition to the obstacles already mentioned, a complicated system like the one in Figure 3 requires the appropriate design tools and methodologies. Cryo-CMOS can use the design automation infrastructure that is already in place for regular CMOS. However, specific issues need to be solved in order to operate at cryogenic temperatures and connect with a quantum system.

### 3.3. Challenges of Cryo-CMOS

- The device-level phenomena that become important at deep cryogenic temperatures and impair the performance and dependability of the circuits, such as greater threshold voltage, hysteresis, kink effects, mismatch, and hot-carrier lifespan degradation.

- The circuit-level trade-offs, such as power consumption, noise, linearity, bandwidth, and gain, that need to be optimized for different applications and specifications of quantum computing systems.

- The system-level integration, such as cosimulation, co-design, and co-verification, of the cryo-CMOS circuits and the quantum processors, that require new methodologies, tools, and standards.

- The temperature range compatibility, such as ensuring that the cryo-CMOS circuits can operate across a wide range of temperatures from room temperature to 4 K or lower.

# 3.4. Specific Issues encountered in Designing Cryo-CMOS Circuits

Some challenges encountered in designing and operating cryo-CMOS circuits are:

- The power dissipation of cryo-CMOS • circuits must be minimized to avoid heating up the quantum processor and degrading its performance. This requires careful optimization of the circuit topology, biasing, and sizing to achieve the desired specifications with minimum power consumption.

- The interconnection and packaging of cryo-CMOS circuits must be compatible with the quantum processor and the cryogenic environment. This requires special materials, techniques, and standards to ensure reliable electrical, thermal, and mechanical performance at low temperatures.

- The device modeling of cryo-CMOS circuits must be accurate and predictive to enable efficient design and simulation. This requires extensive characterization, extraction, and validation of the device parameters and models at cryogenic temperatures.

# 3.5. Implementation of Cryo-CMOS technology in specific quantum computing projects

Some practical examples of how cryo-CMOS technology has been applied in specific quantum computing projects are:

- SeeQC, a quantum computing company, is developing an application-specific integrated circuit (ASIC) quantum computer for drug discovery and development. The ASIC quantum computer uses cryo-CMOS chips that can operate near absolute zero, which is the temperature required for the quantum processor. The cryo-CMOS chips enable the integration of classical control electronics with the quantum processor, reducing the complexity, cost, and power consumption of the system [24].

- Quantum Motion, a quantum computing company, is developing a scalable siliconbased quantum computer using spin qubits. The spin qubits are controlled and read out by cryo-CMOS circuits that can operate at 4 K, which is the temperature required for the quantum processor. The cryo-CMOS circuits exploit the enhanced performance of CMOS transistors at low temperatures, such as reduced noise, increased gain, and reduced power dissipation [25].

SureCore, a low-power memory design company, is developing a cryogenic memory solution for quantum computing applications. The cryogenic memory solution uses cryo-CMOS technology that can operate at 4 K, which is the temperature required for the quantum processor. The cryo-CMOS technology enables the design of low-power, high-density, and stable memory cells that can store and retrieve data for the quantum processor [26].

### 4. Related Works in Quantum Processor

A quantum computer's controller and quantum processor are vital parts. A device that manipulates quantum information employing quantum gates and qubits is known as a quantum processor. A quantum controller is a device that can generate, transmit, and measure microwave signals. And the critical task is to control and read out the qubits in the quantum processor. The following are some publications and works linked to quantum processors and controllers: This article [33] describes a cryogenic integrated circuit that operates at cryogenic temperatures and drives a superconducting processing unit cell using RF and baseband signals. The circuit connected to a two-qubit patch of a 54-qubit Sycamore quantum processor utilizing a 28-nm complementary metaloxide-semiconductor (CMOS) design. This research [34] examines the cryogenic and ambient temperature control methods for superconducting quantum circuits.

| Name                | Developer         | Technology           | Qubits | Quantum<br>Volume | Other Metrics                                                                            | Applications                                   |

|---------------------|-------------------|----------------------|--------|-------------------|------------------------------------------------------------------------------------------|------------------------------------------------|

| Sycamore<br>[27]    | Google            | Super conducting     | 54     | N/A               | Quantum<br>supremacy<br>achieved with 53<br>qubits and 10^9<br>samples in 200<br>seconds | Sampling,<br>optimization,machine<br>learning  |

| Eagle [28]          | IBM               | Super conducting     | 127    | N/A               | N/A                                                                                      | General purpose<br>quantum computing           |

| Advantage<br>[29]   | D-Wave Systems    | Quantum<br>annealing | 5640   | N/A               | 1.4 million CLOPS                                                                        | Optimization,<br>sampling, machine<br>learning |

| lonQ<br>System      | lonQ              | Trapped ions         | 32     | 4 million         | N/A                                                                                      | General purpose<br>quantum computing           |

| Aspen-9<br>[30]     | Rigetti Computing | Super conducting     | 32     | 512               | N/A                                                                                      | General purpose quantum computing              |

| Tangle<br>Lake [31] | Intel Labs        | Super conducting     | 49     | N/A               | N/A                                                                                      | General purpose<br>quantum computing           |

#### Table 1. Existing developments of the Quantum processor

| SV1<br>Processor<br>Service<br>[32] | Amazon Web<br>Services (AWS)<br>Braket and IonQ,<br>Rigetti Computing or<br>D-Wave Systems | Super conducting<br>or trapped ions or<br>quantum<br>annealing | Up to<br>34 | Up to<br>4000 | N/A | Cloud-based quantum<br>computing service for<br>various applications |

|-------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------|---------------|-----|----------------------------------------------------------------------|

|-------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------|---------------|-----|----------------------------------------------------------------------|

The use of single-qubit and two-qubit gates, as well as readout techniques, quantum tomography, feedforward and feedback controllers, are all introduced. Additionally, it offers some possibility for the future creation of expansive, fault-tolerant quantum computer control systems. This article [35] presents a novel technique for the quiet management of a single electron in silicon quantum dots. The method uses an induced gradient electric field known as electric quadrupole spin resonance (EQSR). In terms of scalability, robustness, and speed, the method is superior to already-existing techniques like electron spin resonance (ESR) and electric dipole spin resonance (EDSR). The creation of IBM Quantum System Two, a modular framework for constructing massive quantum computers, is announced in this article. The platform includes the largest superconducting qubit processor to date, the 127qubit Eagle processor. The platform also has a brand-new control system that uses sophisticated signal processing methods to manage up to one million qubits [28].

### 4.1. Limitations and Research gap Regarding Cryo-CMOS

Some of the limitations and the research gap about cryo-CMOS for quantum computing are:

- Cryo-CMOS circuits have to deal with the trade-off between power dissipation and performance. Higher power dissipation can cause self-heating and thermal noise, which can degrade the qubit coherence and fidelity. However, lower power dissipation can limit the speed, bandwidth, and resolution of the cryo-CMOS circuits.

- Cryo-CMOS circuits have to cope with the variability and mismatch of the device parameters at low temperatures. The threshold voltage, mobility, subthreshold slope, and leakage current of the CMOS transistors can change significantly at cryogenic temperatures, depending on the fabrication process, biasing conditions, and device geometry. This can affect the accuracy, stability, and reproducibility of the cryo-CMOS circuits.

- Cryo-CMOS circuits have to overcome the challenges of interconnection and packaging with the quantum processor. The electrical, thermal, and mechanical properties of the materials and components used for interconnection and packaging change low can at

temperatures, causing parasitic effects, thermal gradients, and mechanical stress. This can affect the reliability, scalability, and modularity of the cryo-CMOS circuits.

• Cryo-CMOS circuits have to improve the device modeling and simulation tools for low-temperature operation. The existing device models and simulation tools are mainly developed for room-temperature operation and may not capture the physical phenomena and effects that occur at cryogenic temperatures. This can affect the design efficiency, optimization, and verification of the cryo-CMOS circuits.

### 5. Conclusion

This article covered the promise of cryo-CMOS for the onchip integration of quantum systems, which is motivated by the demand for scalable and effective control and readout of qubits in quantum computing. The research article discussed the difficulties and possibilities of building CMOS circuits at extremely low temperatures, where the characteristics of the devices and the noise sources are different from those at room temperature. In order to enable future quantum computers with millions of qubits, this work demonstrated that cryo-CMOS can provide considerable benefits in terms of power consumption, signal integrity, and system integration. Thus, Cryo-CMOS is a promising technique for integrating quantum systems on chips, but additional study and cooperation are required to realise its potential fully.

#### References

- Kondo Y, Mori R, Movassagh R. Quantum supremacy and hardness of estimating output probabilities of quantum circuits: Proceedings of IEEE 62nd Annual Symposium on Foundations of Computer Science; 2022. p. 1296-1307.

- [2] Yang, Chiribella, Hayashi. Communication Cost of Quantum Processes. IEEE Journal on Selected Areas in Information Theory. 2020; vol. 1: p. 387-400.

- [3] Kandala A, Mezzacapo K, Temme M, Takita M, Brink JM, Chow, Gambetta JM. Hardware-efficient variational quantum eigensolver for small molecules and quantum magnets. In Nature. 2017; Vol 549: p. 242 -250.

- [4] Arute F, Arya K, Babbush R, Bacon D, Bardin JC, Barends R, Biswas R, Boixo S, Brandao FG, Buell DA. Quantum supremacy using a programmable

superconducting processor. Nature Journal. 2019; Vol 574: p. 505–510.

- [5] Monroe C, Meekho D, King B, Itano WM, Wineland DJ. Demonstration of a fundamental quantum logic gate. In Physical review letters.1995; Vol 75: p. 4714-4720.

- [6] Chuang L, Gershenfeld N, Kubinec MG, Leung DW. Bulk quantum computation with nuclear magnetic resonance: theory and experiment: Proceedings of the Royal Society of London. Series A Mathematical, Physical and Engineering Sciences. 1998; Vol 454: p. 447–467.

- [7] Izumi S, Neergaard-Nielsen JS, Andersen UL. Tomography of a Feedback Measurement with Photon Detection: Proceedings of Lasers and Electro-Optics Europe & European Quantum Electronics Conference; 2021. p. 1-1.

- [8] Elzerman R, Hanson Van Beveren LW, Witkamp B, Vandersypen L, and Kouwenhoven LP. Single-shot read-out of an individual electron spin in a quantum dot. Nature Journal. 2004; Vol 430: p. 431–435.

- [9] Paz BC. Coupling control in the few-electron regime of quantum dot arrays using 2-metal gate levels in CMOS technology: Proceedings of IEEE 48th European Solid State Circuits Conference; 2022. p. 45-48.

- [10] Camenzind C, Geyer S, Fuhrer A, Warburton RJ, Zumbühl DM. A spin qubit in a fin field-effect transistor.Natural Electronics. 2021: p. 178-183.

- [11] Petit H, Eenink M, Russ W, Lawrie N. Universal quantum logic in hot silicon qubits. Nature Journal. 2020; Vol 580: p. 355–359.

- [12] Arute F, Arya K, Babbush R, Bacon D. Quantum supremacy using a programmable superconducting processor. Nature Journal. 2019; Vol 574: p. 505–510.

- [13] Vandersypen H. Bluhm H, Clarke J, Dzurak A. Interfacing spin qubits in quantum dots and donors hot, dense, and coherent. npj Quantum Information.2019; p. 34-42.

- [14] Homulle H, Visser S, Patra B. A reconfigurable cryogenic platform for the classical control of quantum processors. In: Review of Scientific Instruments. 2017; Vol 88: p. 045-103.

- [15] Boaventura S. Cryogenic Characterization of a Superconductor Quantum-Based Microwave Reference Source for Communications and Quantum Information. IEEE Transactions on Applied Superconductivity. 2021; vol. 3: p. 1-9.

- [16] Staszewski RB, Homulle HAR, Patra B. Cryo-CMOS Circuits and Systems for Scalable Quantum Computing: Proceeding of International Solid-State Circuits Conference; 2017. p 1-10.

- [17] Muhonen JT. Quantifying the quantum gate fidelity of single-atom spin qubits in silicon by randomized benchmarking. Journal of Physics Condensed Matter. 2015; Vol 27: p. 154-205.

- [18] Chow JM, Gambetta JM, Magesan E, Abraham DW. Implementing a strand of a scalable fault-tolerant quantum computing fabric. Journal of Natural Communication. 2014; Vol 5: p. 40-15.

- [19] Reilly DJ. Engineering the quantum-classical interface of solid-state qubits. npj Quantum Information. 2015; p. 150-168.

- [20] Wang DH. Low-Temperature Deuterium Annealing for the Recovery of Ionizing Radiation-Induced Damage in

MOSFET. IEEE Transactions on Device and Materials Reliability.2013; vol. 23: p. 297-301.

- [21] Ding C, Ngo KD, Lu G. A Soft Magnetic Moldable Composite With Tri-Modal Size Distribution for Power Electronics Applications. IEEE Transactions on Magnetics.2021; vol. 57: p. 1-6.

- [22] Fu X, Riesebos L, Lao L, Sebastiano F, Charbon E. A Heterogeneous Quantum Computer Architecture: Proceeding of ACM International Conference on computing frontiers; 2016. p 1-7.

- [23] Charbon E, Sebastiano F, Patra B. Cryo-CMOS Circuits and Systems for Scalable Quantum Computing: Proceedings of International Solid-State Circuits Conference; 2017. p 1-8.

- [24] Bertels K. Quantum Computer Architecture Toward Full-Stack Quantum Accelerators. IEEE Transactions on Quantum Engineering. 2020; vol. 1: p. 1-17.

- [25] Wu T and Guo J. A Multiscale Simulation Approach for Germanium-Hole-Based Quantum Processor. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 2023; vol. 42: p. 257-265.

- [26] Martiel S, Ayral T, Allouche C. Benchmarking Quantum Coprocessors in an Application-Centric, Hardware-Agnostic, and Scalable Way. IEEE Transactions on Quantum Engineering. 2021. 2, p. 1-11.

- [27] Nirmala P, Asha V, Saju B, Murali SC. Comparative Analysis of Quantum Computing Algorithm: Proceddings of Advanced Computing and Communication Technologies for High Performance Applications; 2023. p. 1-7.

- [28] Wang DS. A comparative study of universal quantum computing models towards a physical unification. Quantum Engineering. 2021; Vol. 85: p 1-14.

- [29] Zeissler K. Controlling a superconducting quantum processor. Natural Electronics. 2023; Vol. 181: p 1-10.

- [30] He Y, Liu J, Zhao C. Control System of Superconducting Quantum Computers. Journal of Superconducting. 2023; Vol 35: p. 11–31.

- [31] Will Gilbert. On-demand electrical control of spin qubits. Nature Nanotechnology. 2023; p 1-15.

- [32] Patra B.: Cryo-CMOS Circuits and Systems for Quantum Computing Applications. IEEE Journal of Solid-State Circuits. 2018; vol. 53 (1): p. 309-321.

- [33] Rietsche R, Dremel C, Bosch S. Quantum computing. Electron Markets.2022; Vol. 32: p. 2525–2536.

- [34] Kanamori, Yoshito, Yoo, Seong-Moo. Quantum Computing: Principles and Applications. Journal of International Technology and Information Management. 2020; Vol. 29: p. 1-8.

- [35] Lao L, van Someren H, Ashraf I, Almudever CG. Timing and Resource-Aware Mapping of Quantum Circuits to Superconducting Processors. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 2022; vol. 41: p. 359-371.